Introducing the 8086 Microcode Browser

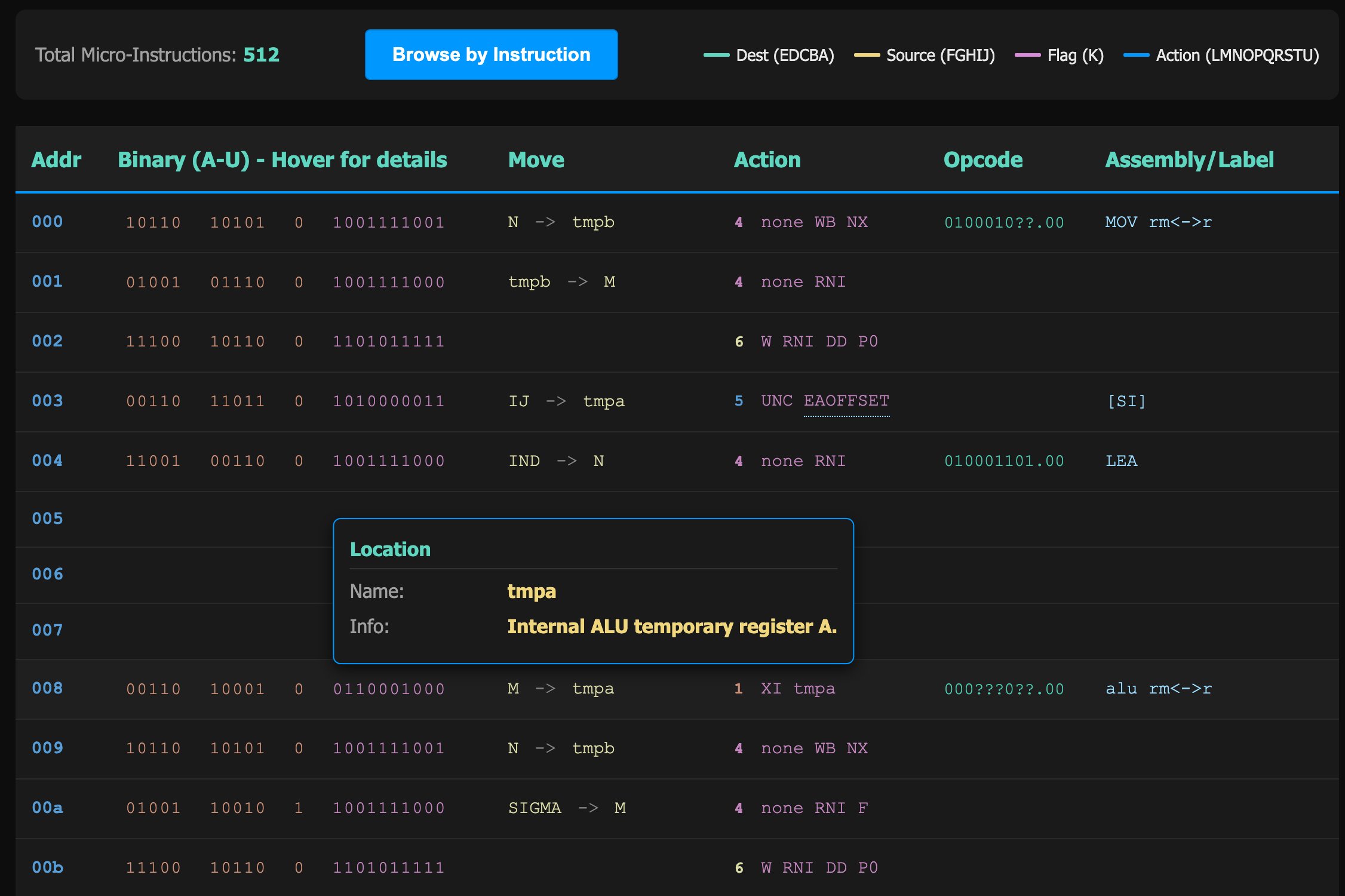

Discover an interactive online browser for the 8086 microcode, meticulously decoded from Andrew Jenner's 2020 extraction. Explore every 21-bit micro-instruction, understand subtle CPU behaviors, and navigate ~300 documented instructions with ease, offering unique insights into the 8086's original design.

Following the release of 486Tang, efforts have been underway to faithfully recreate the 8086 microprocessor, aiming for a design as close as possible to the original chip. This endeavor naturally led to an in-depth exploration of the 8086 microcode, which was expertly extracted and disassembled by Andrew Jenner in 2020.

Like all microcoded CPUs, the 8086 exhibits subtle behaviors beneath its assembly layer. Extensive notes compiled during this study have now evolved into a valuable interactive resource: an online browser for the complete 8086 microcode ROM.

Each 21-bit micro-instruction is meticulously decoded into readable fields. Users can hover over any field to reveal a tooltip explaining its function. All jump targets are interactive, reflecting the 8086 microcode's notable use of indirect jumps, calls, and short branches.

A particularly useful feature is the "Browse by Instruction" option. Activating this provides a list of approximately 300 documented 8086 instructions. Selecting an instruction instantly directs the viewer to its corresponding microcode entry point. With only about 60 unique microcode entry routines internally, this feature significantly streamlines navigation.

Key Characteristics of 8086 Microcode

- Context-Dependent Register IDs: Register identifiers can carry different meanings based on their operational context. For instance, the value

10100signifiesSIGMA(the ALU result) when acting as a source, buttmpaL(the low 8 bits of a temporary ALU register) when used as a destination. - Aliased Registers:

NandRshare the same physical register. Similarly,SIis referred to asIJinternally. This inconsistency in naming conventions within the chip underscores its evolutionary design process. - IP (PC) Behavior: The Instruction Pointer (IP), also known as Program Counter (PC), does not directly point to the next instruction. Instead, it indicates the subsequent prefetch address. The microcode employs a specific micro-operation,

CORR, to reset the IP to the correct next-instruction boundary during branch and interrupt handling. - Arithmetic Instruction Reuse: Most arithmetic instructions leverage the same four micro-instructions (

008–00B). The core functionality is handled by a single micro-operation namedXI, which executes varied arithmetic operations based on the opcode or ModRM bits. This level of elegant reuse is characteristic of 1978 Intel design.